# **RIGA EVENT TIMER IN COMPACT IMPLEMENTATIONS**

In complex systems, a timing block is often required as a compact module that can be built in a common housing together with other functional modules. To meet these requirements we have developed the set of the event timing modules with different performance and precision. The modules also differ with schematic complexity,

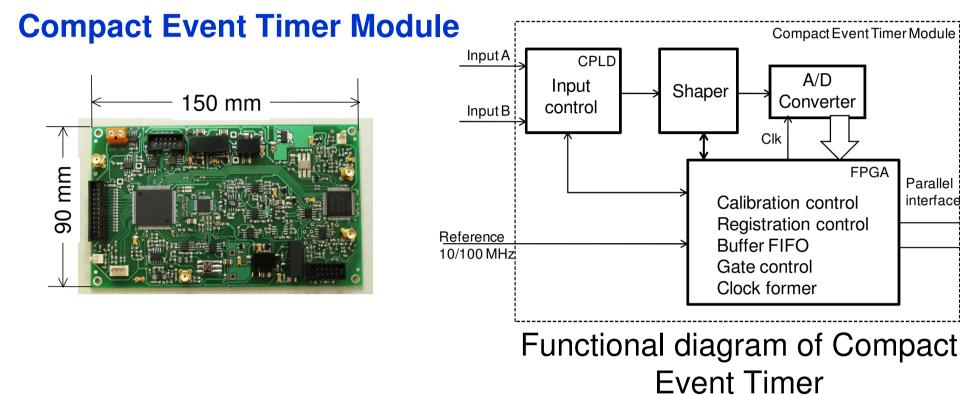

**Compact Event Timer Module** (CETM) provides the same functionality as A033-ET while the size of board is only 90x150 mm and power consumption 4 W. The modified interpolator has deadtime 25 ns providing for measurement rate up to 40 MSPS. This modification allows the wider range of external conditions however degrades the resolution up to 5 ps RMS.

**Doubled Event Timer Module** presents two CETM's integrated into one module.

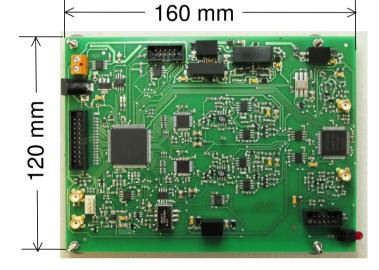

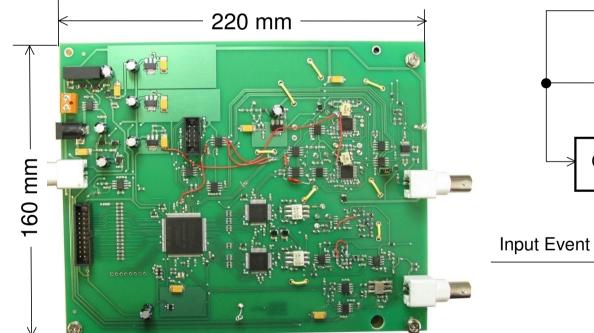

Two separate interpolators for two inputs Start and Stop provide independent registration of events arriving in these inputs allow measuring of zero or negative time intervals between these events. The size of board is 120x160 mm and power Fast Event Timer Module is the timing module providing one channel measurement with very high frequency up to 90 MSP and resolution about 5 ps. In case of low event rates this resolution can be enhanced up to 2.5 ps using the replication possibility. A preliminary size of board is 160x220 mm however it can be essentially minimized. The power

#### sizes and power consumption.

### consumption is about 5 W.

consumption is 8 W.

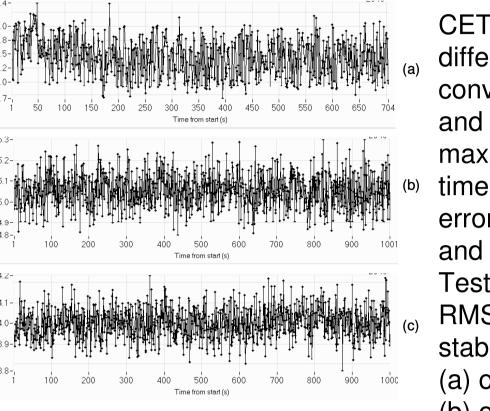

CETMS interpolator has two different time-to-digital conversion schematics for odd and for even events. This allows maximal reducing of the deadtime but increases the random error for interval between odd and even events. Test results on the left show the RMS resolution values and stabilities for intervals between: (a) only odd events; (b) only even events; (c) odd and even events.

#### *Pro:* - compactness: 90x150 mm - small power consumption: 4 W

- the module is ready for operation

- immediately after assembly - fast and stable calibration

- high resolution 4-5 ps RMS

- short dead-time 25 ns

- Contra: essential interval non-linearity for short intervals - two interpolators require two conversion tables and double random error variance

#### *Pro:* - compactness: 120x160 mm - small power consumption: 5 W

- the module is ready for operation

- immediately after assembly

- fast and stable calibration

- high resolution 5-6 ps RMS

- no dead-time for different inputs

- Contr: RMS resolution degradation up to 8 ps for intervals less than 30 ns.

- essential interval non-linearity for short intervals

- two interpolators require two conversion tables and double random error variance

## **Doubled Event Timer Module**

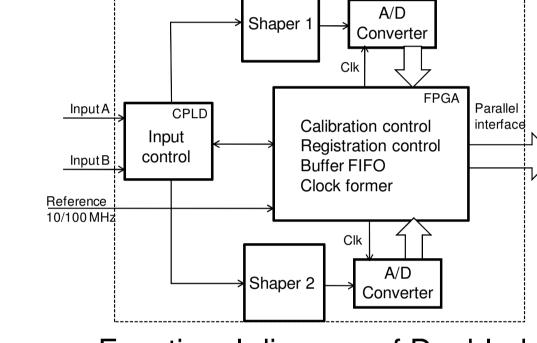

Functional diagram of Doubled **Event Timer**

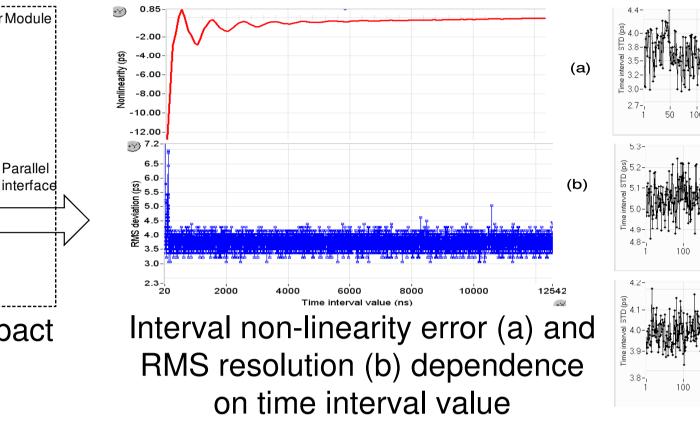

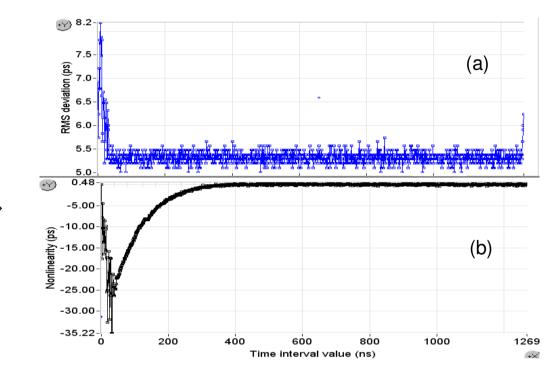

Interval non-linearity error (a) and RMS resolution (b) dependence on time interval value

DETM incorporates two CETMs with one shared CPLD for input control and one FPGA for parallel functionality. DETM development was aimed to time almost simultaneous events which are typical for Positron Emission Thomography devices in medicine and particle registration in nuclear physics.

In the DETM each interpolator has just one time-to-digital conversion schematic and provides the RMS resolution 4 ps but for Start-Stop intervals the error variance is summed from both interpolators and resulting RMS resolution is 5.5 ps.

For short intervals less than 30 ns this resolution degrades up to 8 ps because of cross-correlation of close events.

The same effect impacts to the non-linearity error but it can be identified simultaneously with the channel-to-channel offset and corrected in the interval calculation.

#### **Fast Event Timer Module**

**Doubled Event Timer Module**

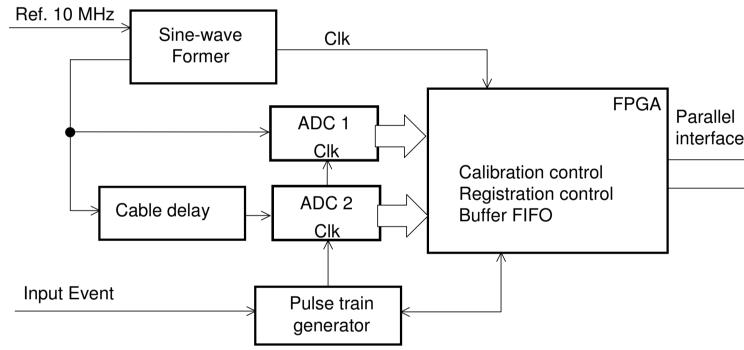

FETM is built on the basis of timing technology that differs from A033-ET technology. It uses a

Functional diagram of Fast Event Timer

output

Stop

digital sampling of the stable sine-wave functions in time instants directly related to arriving of input events. This allow increasing measurement rate up to hundreds millions time-tags per second.

The developed pilot version can register up to 90,000,000 time-tags/sec and has an additional feature allowing to improve the RMS resolution from 5 ps for event rate 90 MHz to 2.5 ps for event rate less than 20 MHz.

FETM development was aimed to applications where increasing of timed events frequency allows increasing received or transferred data volume. The Data transfer via Laser link, LIDAR system, 3D-Scan system are such system which performance is defined by data acquisition rate and timing precision.

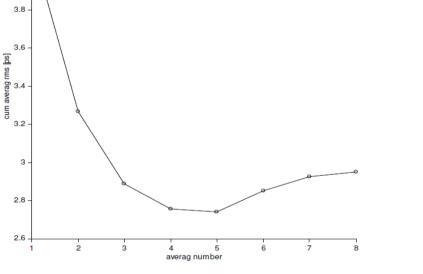

RMS resolution dependence on the number of refining pulses that are generated until an arrival of next event. It is seen that in this module the refinement is effective until the forth refining pulse.

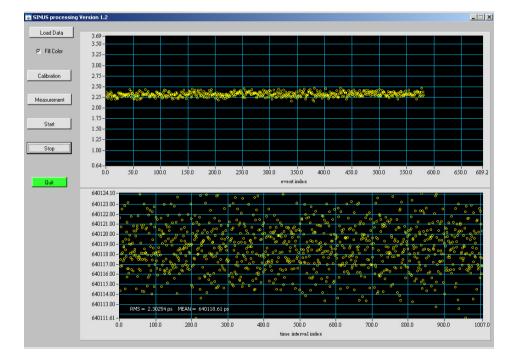

RMS resolution stability (upper) and measured time interval values (bottom). The time 640 ns between events allows to refine the time-tags and to get resolution 2.3 ps (including test generator instability).

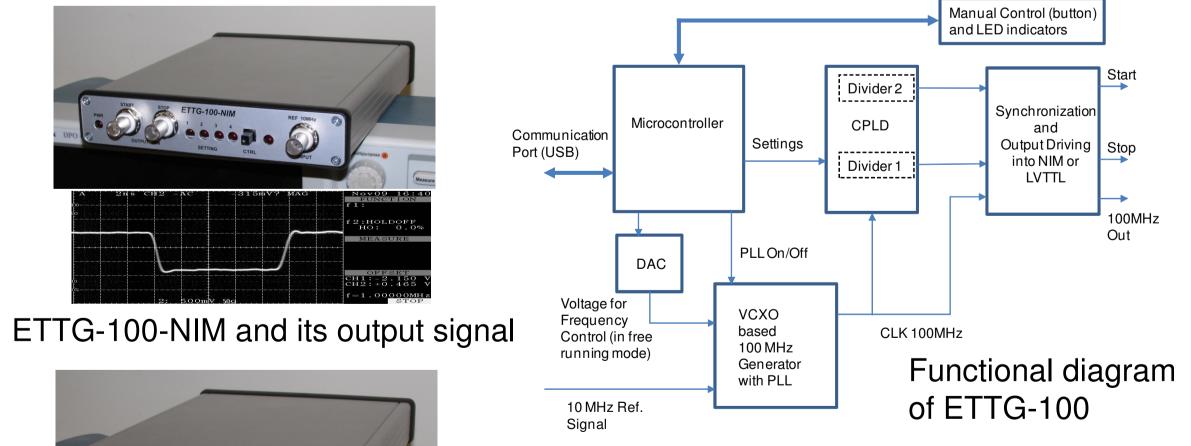

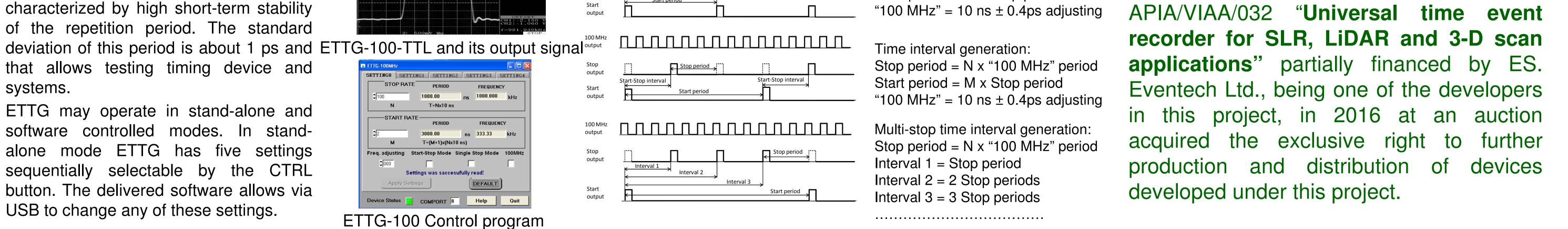

**Event Timer Test Generator** ETTG-100 is designed for estimation of precision parameters of Event Timers and similar timing devices (Time Interval Counter, Time Analyzer, Time-to-Digital Converter) having a picosecond resolution of time measurements. In accordance with existing standards for inputs of timing devices, the Generator ETTG-100 has two modifications:

ETTG-100-NIM generating negative pulses in NIM standard, and

- ETTG-100-TTL generating positive pulses in LVTTL standard.

ETTG generates periodic sequences,

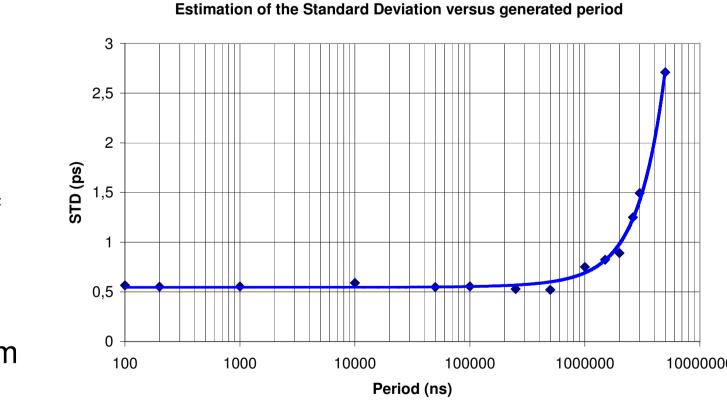

Experimental estimation of the ETTG period stability in the range of periods from 100 ns up to 5 ms. Experimental points present STD averaging on ~500 STD values, when each of them is estimated on the array of 1000 measured periods.

Three generation modes and their time diagrams  $\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}\underline{\mathsf{n}}$ Period generation: Stop period = N x "100 MHz" period Stop period Start period = M x Stop period ← Start period →

This poster reflects the research results that were obtained in the framework of the R&D project No. 2013/0036/2DP/2.1.1.1.0/13/

E. Boole, V.Bespalko, A.Rybakov, V.Vedin, Institute of Electronics and Computer Science; buls@edi.lv; R. Spunde (Eventech Ltd., Riga, Latvia; r.spunde@eventechsite.com)

2017 ILRS Technical Workshop – October 2 – 5, 2017