Eiropas Reģionālā attīstības fonda (ERAF) programmas “Izaugsme un nodarbinātība” 1.2.1. specifiskā atbalsta mērķa “Palielināt privātā sektora investīcijas P&A” 1.2.1.2. pasākums “Atbalsts tehnoloģiju pārneses sistēmas pilnveidošanai” projekts „Silīcija Intelektuālā Īpašuma Izstrādes Nams” (SilHouse) identifikācijas Nr. KC-PI-2020/12. Līgums ar Latvijas Investīciju un attīstības aģentūru (LIAA) par dalību tehnoloģiju pārneses pasākumā Nr. KC-L-2017/14.

Priekšvēsture

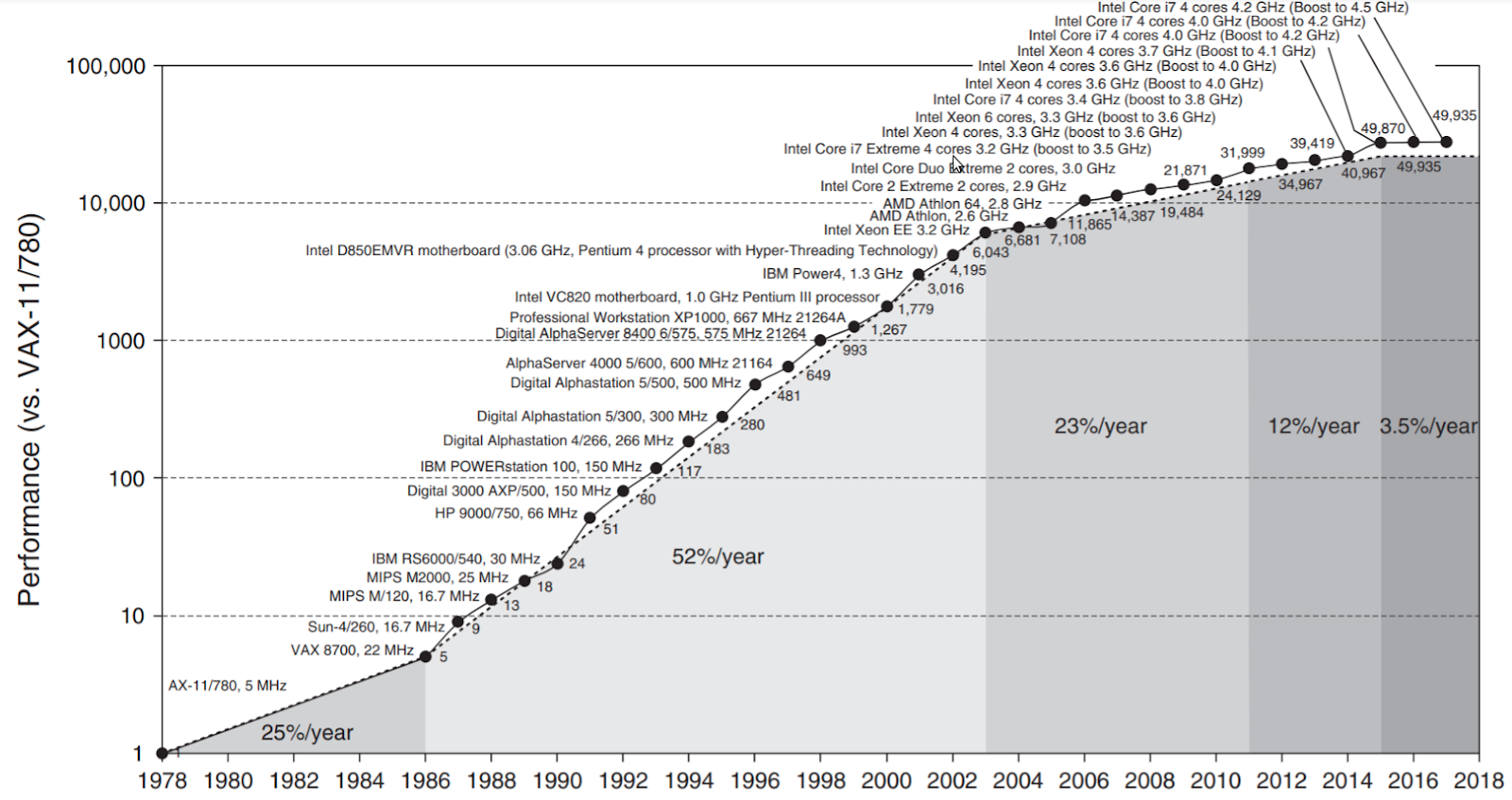

1965. gadā amerikāņu inženieris un uzņēmējs Gordons Mors (Gordon Moore) žurnāla rakstā ar nosaukumu “Cramming more components into integrated schemes (Iespiest vairāk komponenšu integrālās shēmās)” izteica pareģojumu, kas ietekmēja IC (Integrated Circuit – integrālo shēmu) attīstību. Viņš paredzēja, ka tranzistoru skaits, kas tiks “iespiesti” IC, katru gadu dubultosies un prognozēja, ka šī tendence turpināsies vismaz turpmākos desmit gadus. 1975. gadā viņš mainīja savu apgalvojumu, kā rezultātā viņš postulēja empīrisku novērojumu, kuru tagad pazīstam kā Mūra likumu (Moore’s Law), – tranzistoru skaits IC divkāršojas ik pēc diviem gadiem. Pieaugot tranzistoru skaitam, Mūra kolēģis Deivids Hauss (David House) prognozēja, ka datora mikroshēmu veikspēja dubultosies ik pēc 18 mēnešiem.

Procesora veiktspējas pieaugums, kas tika novērtēts, izmantojot SPEC veselu skaitļu aprēķinu testu

(iekrāsotajās sadaļās ir redzams veiktspējas procentuālais pieaugums gadā).

Ņemot vērā, ka tranzistoru blīvums integrālajās shēmās turpina atpalikt no tā, ko Mūra likums paredzēja kopā ar ikgadējo procesora veiktspējas pieauguma kritumu, mēs sākam ieiet periodā, ko daži sauc par Pēc Mūra likuma ēru.

Tagad rodas jautājums – kāda ir skaitļošanas tehnikas nākotne? Kamēr kvantu skaitļošana vēl ir ceļā, nākamais solis, lai palielinātu skaitļošanas veiktspēju, ir izstrādāt jomai specifiskas arhitektūras (domain-specific architectures) jeb jomai specifiskus paātrinātājus (domain-specific accelerators). Paātrinātāji ir pielāgotas digitālas shēmas, kuras paātrina noteiktas lietojumprogrammas daļas, tādejādi pārspējot vispārīga lietojuma procesorus.

Mērķis

Nodrošināt pielietojumspecifisku paātrinātāju risinājumus, lai apmierinātu pašreizējo pieprasījumu pēc augstas veiktspējas, zema latentuma un energoefektīvas skaitļošanas, vienlaikus samazinot izstrādes laiku un izmaksas.

Tehnoloģija

SilHouse projekts fokusējas uz datorredzes IP kodolu jeb domēn-specifisku paātrinātāju komercializāciju. IP kodolu uzņemšanai tirgū, projekta ietvaros tiks modificēti IP kodoli EDI īpašumā, kā arī izstrādāti rīki datorredzes algoritmu paātrinātāju komplektācijai, kas nodrošinās to integrēšanu esošajās, uz datorredzi balstītās, sistēmās. Uz doto brīdi EDI jau ir izstrādājis IP kodolus visdažādāko algoritmu realizācijai:

– Attēla transformācija (ar digitālu tālummaiņu un logu veidošanas (windowing) funkcijām),

– Aparatūras bikubiska (augstas kvalitātes) attēla interpolācija (kā daļa no attēla transformācijas kodola, bet to var atdalīt),

– Bayer kameras sensora attēla debabūšana/demosaicing,

– Mirušo pikseļu korekcija,

– Histogrammas korekcija un linearizācija,

– Attēlu filtrēšana (pilnībā konveijerizēts, zems latentums, attēlu konvolūcija ar kodolu),

– Stacionārā trokšņa (fixed-pattern noise) korekcija,

– u.c.

Komercializācijas modelis

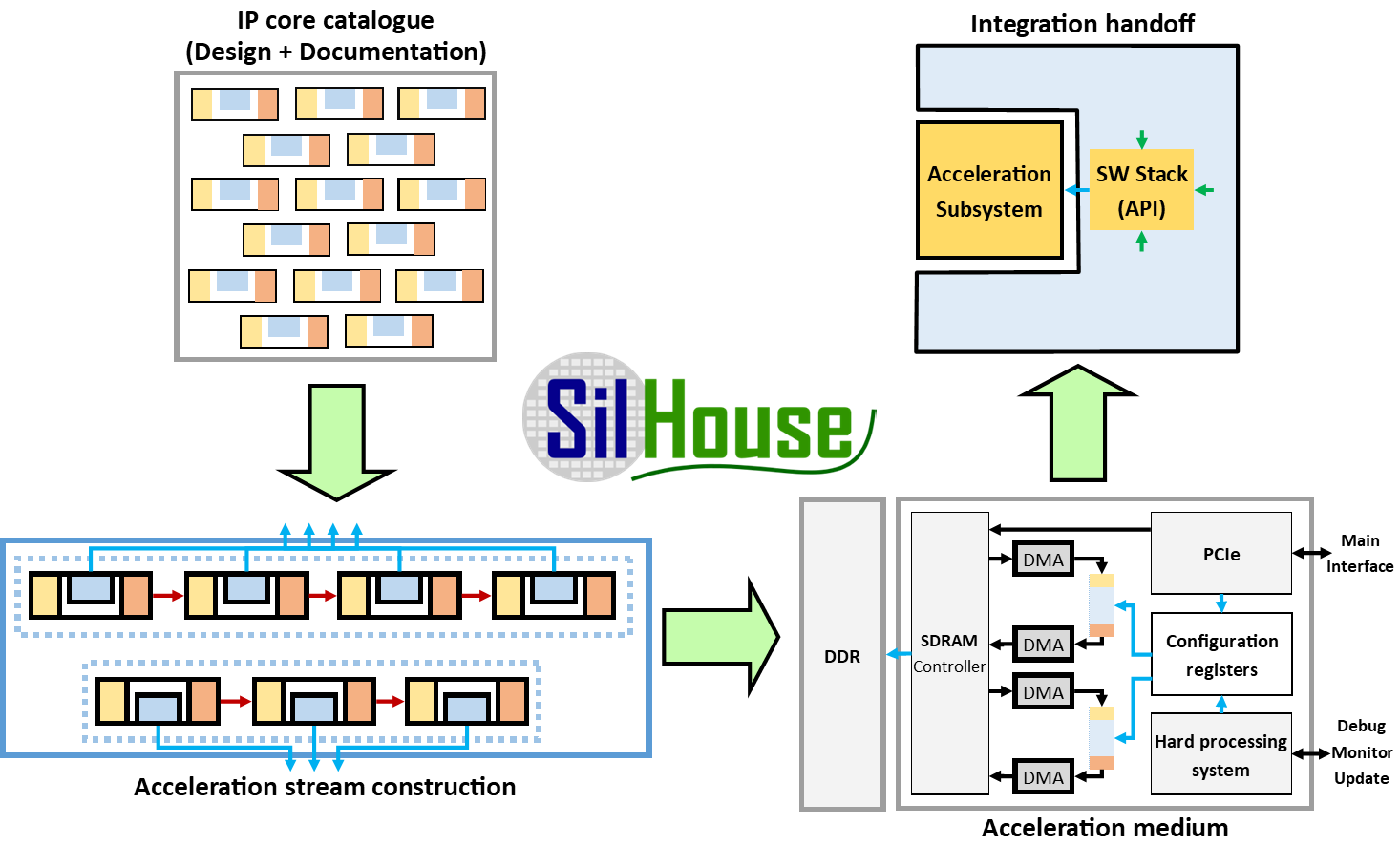

SilHouse projekta paātrinātāju sistēmau izstrādes konceptuālais risinājums.

SilHouse projekta paātrinātāju sistēmau izstrādes konceptuālais risinājums.

Paātrinātāju konstrukcijas process var tikt sadalīts četros posmos:

1. IP pamatkatalogs: Nodarbojoties ar datoredzes un signālu apstrādes pētniecību, EDI ir izstrādājis daudzas specializētas komponentes jeb IP kodolus, tai skaitā lēcu kropļojumu korekcijas, attēlu transformācijas, pazīmju ekstrakciju. Komponenti ir veidoti, ņemot vērā modularitāti, tāpēc tie ir veidoti ar kopēju datu apmaiņas saskarni. Tas ļauj viegli savstarpēji savienot visas komponentes. Protams, vispārējais projektēšanas process neaprobežojas tikai ar EDI IP kodolu izmantošanu, bet var izmantot arī citu piegādātāju IP kodolus.

2. Paātrinājuma plūsmas komplektācija: Pēc noteiktajām prasībām no mūsu IP pamatkataloga izvēlamies nepieciešamos komponentus un nepieciešamības gadījumā izstrādājam trūkstošos, lai izveidotu datu apstrādes konveijeru definētajam uzdevumam. Izmantojot mūsu IP pamatkataloga sastāvdaļas, mēs samazinām izstrādes laiku un izmaksas, kas tam būtu nepieciešamas, ja tās būtu jāprojektē no jauna.

3. Paātrinājuma vide: Kad datu apstrādes konveijers ir gatavs, mēs izstrādājam vai pielāgojam jau izgatavotu akseleratora platformu integrācijai attiecīgajā vidē. Izstrādātā platforma darbosies vai nu kā atsevišķa platforma, vai kā papildierīce gadījumā, ja atjauninām esošo sistēmu. Pēdējā gadījumā akseleratora platformai būtu piemērota sakaru saskarne datu apmaiņai starp akseleratoru un sistēmu, piemēram, PCIe, USB, Ethernet u.c.

4. Integrācijas nodošana klientam: Platforma ar izstrādāto paātrinātāju un ar to saistītajām programmatūras bibliotēkām ir gatava integrēšanai sistēmā. Programmatūras bibliotēkas un dokumentācija nodrošina vienkāršu un ātru integrāciju esošajā sistēmā.

Projekta galvenie tehniskie uzdevumi

– Atmiņas tiešpiekļuves kodolu izstrāde;

– Intelektuālā īpašuma aizsardzības mehānismu izstrāde;

– Komplektācijas rīku un pieeju izstrāde;

– Dokumentācijas veidošana;

– Linux dziņu un bibliotēku programmatūras veidošana;

– Pieejas verifikācija silīcijā (pielietojumspecifisku čipu izstrāde).

Laika periods: 01.01.2021 – 31.03.2021

Veikta apzināšana un noorganizētas tikšanās ar vietējiem uzņēmējiem ar mērķi prezentēt tehnoloģiju un atrast tai jaunus pielietojumus. Izmantojot EDI gūtos kontaktus starptautiskos pētniecības projektos tika apzināts starptautisks eksperts ar komercializējamo tehnoloģiju saistītu pieredzi akadēmiskajā un jaunuzņēmumu vidēs.

Ar tehnoloģijas prezentēšanu tirgū saistīto materiālu izveide (tiešsaistes profils, informatīvie materiāli).

Projekts tika pārstāvēts EDI komercializācijas projektu prezentācijās LIAA pārstāvniecību ārzemēs vadītājiem, kas deva iespēju to prezentēt Somijas VVF pētniekiem.

Periodiski izvērtēta informācija un jaunās tehnoloģijas, kuras varētu ietekmēt komercializācijas gaitu.

Laika periods: 01.04.2021 – 30.06.2021

Tiešsaistes dalība Hannover Messe izstādē, ar mērķi meklēt potenciālos ārzemju partnerus.

Tiešsaistes un klātienes prezentācijas potenciālajiem partneriem.

Potenciālo partneru/klientu uzrunāšana e-pastos.

Dalība LIAA komercializācijas veiksmes stāstu prezentācijās

Tiešsaistes tikšanās ar Amerikas latvieti un komercializācijas eksperti Karīnu Sotņik.

Aukstie zvani un e-pasti.

Laika periods: 01.07.2021 – 30.09.2021

Iepazīšanās ar Embedded vision konferences digitāli pieejamajiem materiāliem.

Izpētītas WIPO rekomendācijas un labās prakses IĪ komercializēšanai un zināšanu pārnesi.

Zvans ar LIAA Somijas pārstāvi par sadarbību ar Somijas uzņēmumiem no fotonikas klāstera

Aukstie zvani un e-pasti.

Dalība EMVA Spotlight vebinārā

Laika periods: 01.10.2021 – 31.12.2021

Tiek izstrādāts dokuments, kas potenciālajiem klientiem rastu skaidrību par produkta / servisa izmantošanas iespējām un izmaksām (Offer Matrix);

Veikta analīze par Zviedrijas un Vācijas fotonikas klāsteru kompānijas;

Turpināta epastu izsūtīšna kontaktiem, kuri GITEX izstādēs;

Ir nodibināts kontakts ar EMVA (European Machine Vision Association) par biedru kontaktu iegūšanu un iespēju EDI iegūt asociācijas biedra statusu;

Periodiski izvērtēta informācija un jaunās tehnoloģijas, kuras varētu ietekmēt komercializācijas gaitu, tādos resursos kā www.design-reuse.com un www.eetimes.com.

Tika veikta vizīte pie klienta Latvijā, kur viņiem tika nodota EDI izstrādātā risinājuma prototips, tā dokumentācija, kā arī nokārtoti dokumenti IP aizsardzībai un iekārtas nodošanai;

Komunikācijas ar LIAA par spin-off uzņēmuma veikšanas iespējām (kā tas ir atrunāts projekta pieteikumā) un citiem derīgiem komercializācijas variantiem;

Gatavošanās un dalība konferencē “Optics and Photonics days (OPD2021)“ Turku, Somija.

Darbs ar potenciālo klientu Latvijā

Mārketinga un produktu materiālu atjaunošana

Dalība EMVA Spotlight vebinārā

Aukstie zvani un e-pasti.

Laika periods: 01.01.2022 – 31.03.2022

Periodiski izvērtēta informācija un jaunumi kuri varētu ietekmēt komrecializacijas gaitu tādos resursos kā www.design-reuse.com un www.eetimes.com

Turpinās komunikācija ar konferencē “Optics and Photonics days (OPD2021)“ Turku, Somijā iegūtajiem kontaktiem.

Turpinās darbs ar Latvijas uzņēmumu risinājuma testēšanā un pilotēšanā.

SilHouse tehnoloģijas apraksta un IP aizsardzības stratēģijas sagatavošana.

Atkārtota saziņa ar vairākiem uzņēmumiem Latvijā, kas izrādījuši interesi par risinājumu.

Uzsākta dalība un D&R un publicēta informācija par pirmo komercializējamo IP kodolu.

Dalība EMVA Spotlight vebinārā.

Laika periods: 01.04.2022 – 30.06.2022

Sagatavots saraksta ar Vacijas un Nīderlandes uzņēmumiem, ar kuriem EDI būtu interese sadarboties. Tas kopā ar informatīvajiem materiāliem nodots LIAA.

Periodiski izvērtēta informācija un jaunumi kuri varētu ietekmēt komrecializacijas gaitu tādos resursos kā www.design-reuse.com un www.eetimes.com

Turpinās komunikācija ar konferencē “Optics and Photonics days (OPD2021)“ Turku, Somijā iegūtajiem kontaktiem.

Turpinās darbs ar Latvijas uzņēmumu risinājuma testēšanā un pilotēšanā.

SilHouse tehnoloģijas apraksta un IP aizsardzības stratēģijas sagatavošana.

Sagatavošanās un dalība Hannover Messe izstādē. Komunikācija ar gūtajiem kontaktiem

Dokumentācijas sagatavošana EDI tehnoloģijas izsolē

Otra IP kodola publicēšana D&R datu bāzē.

Dalība FIT-4-NMP darbnīcā/seminārā

Sazvans ar uzņēmumu un tehnoloģijas prezentācija tehnoloģijas pielietošanai vision-in-loop risinājumos.

E-pasti interesentiem, kas EDI IP kodolus apskatījuši D&R datu bāzē

Laika periods: 01.07.2022. – 31.10.2022.

Periodiski izvērtēta informācija un jaunumi kuri varētu ietekmēt komrecializacijas gaitu tādos resursos kā www.design-reuse.com un www.eetimes.com

Risinājuma pielāgošana demonstrācijām klientiem, vairāku paātrinātāju plūsmu iespējošana, risinājuma pārkonfigurēšanas pieejas uzlabošana un atkļūdošana; tehnoloģijas vispārīgās veiktspējas uzlabošana;

Saziņa ar uzņēmumu un tehnoloģijas prezentācija tehnoloģijas pielietošanai vision-in-loop risinājumos;

Komunikācija un tehnoloģijas prezentācijas vairākiem potenciālajiem interesentiem

Komunikācija ar potenciālajiem klientiem, kuri izrādījuši interesi par publicētajiem silīcija intelektuālā īpašuma kodoliem (D&R datubāzē);

Tikšanās un prezentācija Itālijas investīciju grupai;

Sagatavota nepieciešamā dokumentācija un tehnoloģijas izsoles rīkošana;

Potenciālo klientu informēšana par izsoli;

—

Saskaņā ar komercializācijas stratēģiju, projekts tiek uzskatīts par komercializētu.

Visus interesentus, kam ir interese par tehnoloģiju, pēc projekta noslēguma, aicinām rakstīt info@edi.lv (e-pasta tēmā norādot: SilHouse tehnoloģija) vai apmeklēt Design & Reuse:

(1) https://www.design-reuse.com/sip/axi4-memory-mapped-to-from-axi4-stream-dma-ip-51752/

(2) https://www.design-reuse.com/sip/spatial-image-transformation-accelerator-ip-51037/